在半导体芯片不断追求微型化的进程中,从微米级到纳米级制程的跨越,带来了性能的飞跃,也埋下了可靠性的隐忧。其中,电迁移作为金属互连结构中最关键的失效机制,直接关系到芯片能否长期稳定运行,甚至成为先进制程芯片能否大规模商用的核心制约因素。

简而言之,半导体领域的电迁移,是指在芯片内部极高的电流密度作用下,金属原子(如铝、铜)发生定向迁移,导致互连结构性能衰退乃至失效的现象。这个过程贯穿了半导体设计、制造与封装的每一个环节。

电迁移:发生在芯片“神经网络”里的原子迁徙

如果把芯片中的晶体管比作开关,那么连接这些开关的金属互连线就是复杂的神经网络,负责信号传输和供电。而电迁移,就发生在这张网的核心区域,主要涉及芯片制造的后端互连工艺。

其本质可以理解为“电子风”吹动原子的过程。当电流通过金属线时,高速流动的电子会与金属原子发生碰撞,传递动量。当这种“电子风力”足够大,大到能克服原子在晶格中的束缚时,原子就会顺着电子流的方向开始“搬家”。结果就是,在电流流出的区域,原子流失形成空洞;在电流流入的区域,原子堆积形成小丘。在芯片内部,以下几个区域是电迁移的“重灾区”:

电源分配网络:承担着为整个芯片供电的重任,电流密度最高。

时钟信号线:高频工作下,电流波动剧烈,加剧了原子的迁移。

通孔与金属线的连接处:这里是不同层金属的交汇点,界面复杂,缺陷较多,原子更容易扩散。

芯片与封装的互连焊盘:既要承受电流,又要承受温度,风险显著提升。

微观世界里的“三股力”:电迁移如何发生?

1. 电子风力

当芯片工作时,互连线上的电流密度可以高达每平方厘米数百万安培。在如此高的电子流冲击下,金属原子就像被狂风卷起的沙粒,不断受到碰撞而获得定向移动的能量。尤其是在7纳米及以下的先进制程中,线宽仅有几个纳米,电子与原子的碰撞概率大幅增加,“电子风”的驱动作用更为显著。

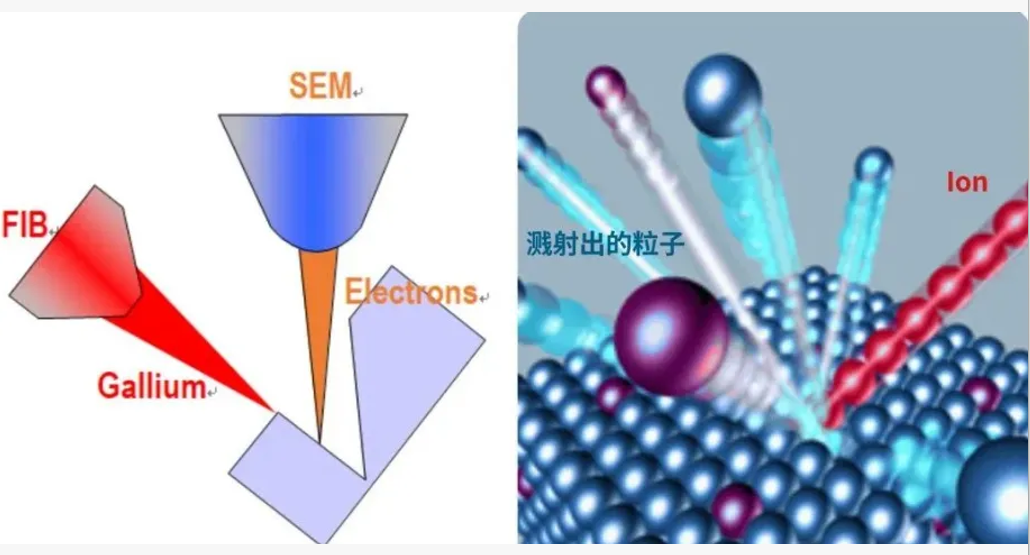

2. 界面与晶界的“快车道”

芯片内部的金属互连并非单一的均匀结构。它是由金属线、阻挡层、介质层构成的多层复合体,层与层之间存在大量界面。同时,金属本身是多晶体,晶粒与晶粒之间的晶界处原子排列松散,扩散阻力小。因此,界面和晶界就成了原子迁移的“高速公路”,迁移速率远高于晶粒内部。这也是为什么制造工艺中,界面优化是提升抗电迁移能力的关键。

3. 温度与电场的“协同催化”

芯片工作时,晶体管本身会发热,而互连线上的大电流又会产生焦耳热,导致局部温度升高。高温使金属原子热振动加剧,更容易脱离晶格束缚。与此同时,互连线上的电场也会直接作用于金属离子,形成电场力。这股力量与“电子风力”协同,加速了原子的定向迁移。对于高性能CPU或GPU,局部热点温度轻易就能超过100℃,此时电迁移速率会呈指数级增长,大大缩短芯片寿命。

当原子“搬家”之后:芯片失效的三种方式

1. 空洞形成,电路中断

原子源源不断地迁走,会在源头留下大量空位。这些空位逐渐汇聚、长大,最终形成空洞。空洞的出现,使金属互连线的有效截面积变小,电阻升高。当空洞扩大到足以切断连线时,电路就会彻底断开。这是最常见的电迁移失效形式,直接导致芯片供电中断,功能丧失。

2. 小丘生长,相邻短路

迁走的原子并非消失,而是在下游堆积。当堆积量超过金属线的容纳极限时,就会在表面形成凸起的小丘甚至细长的晶须。在先进制程中,相邻金属线的间距仅有几十纳米,这些小丘很容易搭到旁边的线上,造成短路。这种短路会引发信号干扰、逻辑错误,严重时甚至可能烧毁芯片。

3. 电阻漂移,性能衰退

即便没有形成开路或短路,在空洞形成和小丘生长的过程中,互连线的截面积在不断变化,导致电阻持续漂移。电阻的变化会带来两个直接后果:一是信号传输延迟增加,可能导致芯片时序混乱,运算出错;二是供电网络的电压降增大,供电不稳定,芯片性能出现波动。这种渐进式的衰退,对追求长期稳定性的车规级、工业级芯片而言,是绝对无法接受的。

谁能影响电迁移?

1. 设计层面

线宽越窄,电流密度越高,电迁移风险越大。同时,布线中的拐角、分支、通孔等位置,容易出现电流集中,成为薄弱环节。合理的电源网络拓扑设计,能有效分散电流,降低局部风险。

2. 工艺层面

金属沉积的均匀性决定了晶粒大小,晶粒越大、晶界越少,抗电迁移能力就越强。阻挡层的沉积质量、通孔的刻蚀精度,都会影响互连结构的完整性,从而影响原子的扩散路径。

3. 材料层面

从铝到铜的升级,是半导体行业对抗电迁移的一次重大胜利,铜的抗电迁移能力是铝的十倍以上。如今,通过在铜中添加少量其他金属形成合金,或在其表面覆盖一层钴、钌,可以进一步增强原子的束缚力。此外,低k介质的导热性能,也会间接影响互连温度,进而影响电迁移速率。

4. 应用层面

芯片的工作环境直接决定了其电迁移寿命。服务器CPU常年高负载运行,高温、高电流密度下,寿命挑战最大。车规芯片则要面对-40℃到150℃的剧烈温度波动,冷热循环会加速界面缺陷的产生,加剧电迁移。

全链条出击:半导体行业如何应对电迁移?

1. 设计优化,源头规避

在芯片设计阶段,通过严格的设计规则约束线宽和电流密度。对高风险区域采用冗余设计,增加线宽或并行布线。同时,借助先进的仿真工具,提前对电源网络、时钟线等关键路径进行电迁移寿命校核,优化布线方案。

2. 工艺升级

在制造环节,通过优化金属沉积工艺获得更大晶粒尺寸的金属层,减少晶界。引入合金化和覆盖层技术,抑制原子表面扩散。优化阻挡层工艺,增强界面结合力。并不断提升工艺精度,减少互连结构中的先天缺陷。

3. 封装助攻,散热与稳定

封装环节也在积极应对。采用倒装、硅通孔、系统级封装等先进技术,缩短互连距离,降低电阻和电流密度。同时,使用高导热材料,提升散热效率,为芯片“降温”,从源头上抑制电迁移。

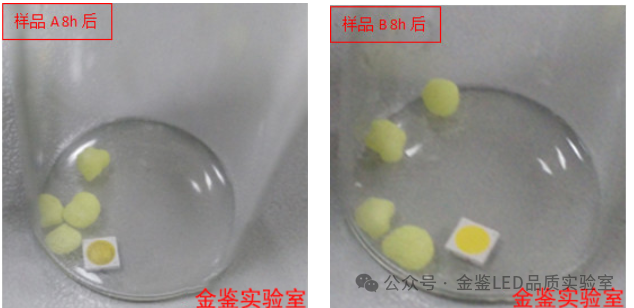

4. 严苛验证,确保可靠

每一颗芯片在出厂前,都要经过严格的可靠性验证。通过加速寿命试验,在高温、高电流密度下让芯片“加速老化”,推算出其在正常工作条件下的寿命。同时,还要进行冷热循环、高温老化等测试,模拟真实应用场景,确保万无一失。

随着半导体制程迈向3纳米、2纳米,电迁移的挑战也愈发严峻。线宽不断缩小,电流密度急剧攀升;低k介质导热性差,热点难以散发;3D堆叠技术使互连结构空前复杂。这些都让电迁移问题变得更加棘手。

为此,行业也在探索新的方向。一方面,寻找钌、钼等新型互连材料,以期替代铜;另一方面,利用人工智能结合工艺数据,在设计阶段更精准地规避风险。同时,Chiplet等先进封装技术通过模块化设计分散电流负载,也是重要的解决思路。未来,甚至可能出现能够实时监测芯片状态、提前预警电迁移隐患的智能可靠性技术。

发表评论 取消回复