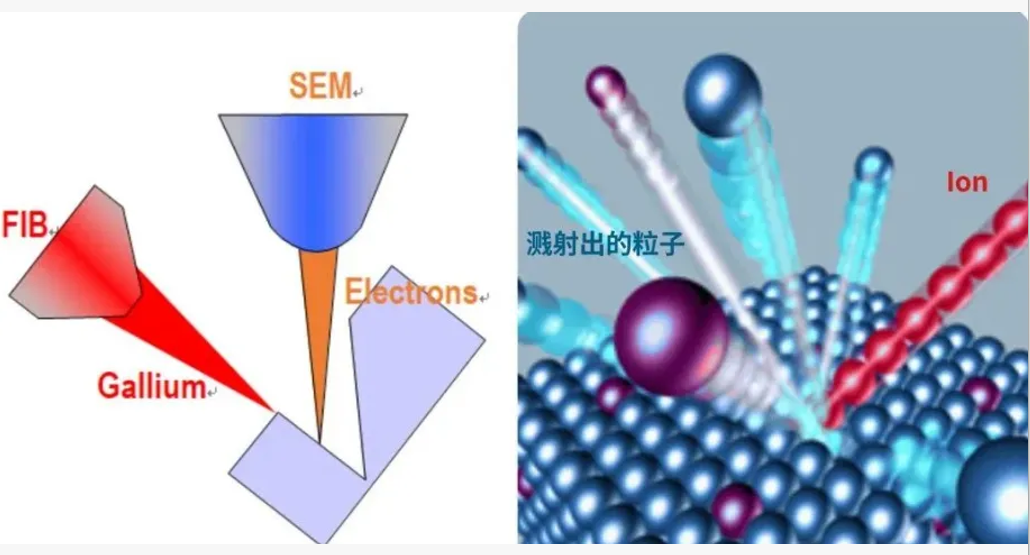

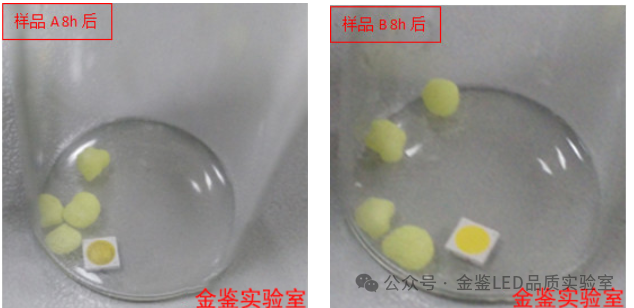

静电在自然界中无处不在。从芯片制造、封装测试、运输存储到组装使用,静电可能在任一环节对芯片造成不可逆损。(1)人体通常需2~3KV静电才能感知,而现代半导体器件可能仅需不到20V即会受损。(2)在无尘室中,技术人员身着防静电服时,仍可能携带足以损伤芯片的静电。(1)部分受损元器件外观完好,初始功能正常,却已留下“内伤”。(2)此类产品可通过常规检测出厂,但在实际使用中(1周至6个月内)易提前失效。(1)从芯片生产到使用寿命结束,静电威胁可能来自人体、设备、环境等各方面。(2)静电产生的不确定性导致质量问题难以系统性预防与追踪。(1)静电损伤的失效分析需借助扫描电镜等高精密仪器,耗时耗力。(2)部分损伤特征易被误判为“早期失效”或“原因不明失效”,掩盖真相。(1)随着晶体管特征尺寸缩小,芯片ESD防护能力持续减弱。(2)65nm至90nm工艺节点下,栅氧化层厚度小于2nm,击穿电压降低,对ESD保护电路提出更高要求。(1)轻掺杂漏技术易引发尖端放电,使MOS管更易被静电击穿。(2)硅化物工艺为静电电流提供进入芯片内部的路径,增加损坏风险。(1)市场对防护等级要求提升,迫使设计人员开发更优异的ESD防护方案。(2)从0.18微米工艺节点开始,专用定制方案比例增加,显著推高设计成本。面对日益严峻的静电挑战,ESD防护电路设计需要遵循五个基本原则,这些原则共同定义了ESD防护的设计窗口。1. 正常状态下的关闭特性。在无ESD事件发生时,保护器件必须保持关闭状态,任何误触发都可能导致核心电路功能异常。2. 快速响应能力。当芯片遭遇ESD事件时,保护器件必须在纳秒级时间内迅速开启,特别是应对快速的器件充电模型事件。响应速度的丝毫延迟都可能导致核心电路损毁。3. 电压钳位能力。ESD事件期间,芯片管脚上的总电压(包括保护器件上的电压与金属互连线上的电压)必须不超过核心电路的耐受极限,否则将造成不可逆损伤。4. 鲁棒性。在设计的ESD保护等级下,防护电路本身必须能够承受静电冲击而不损坏,这关系到器件在真实环境中的生存能力。5. 自恢复功能。确保系统持续稳定运行。ESD事件结束后,保护器件应能自动返回关闭状态,避免进入闩锁状态而导致电路故障。基于这些原则,可以明确ESD防护电路的安全设计窗口:防护电路的开启电压必须低于内部器件栅氧化层的击穿电压;保持电压需高于电路正常工作电压,防止误开启;工作电流应小于器件的热失效电流,避免二次击穿。随着工艺节点不断缩小,ESD设计窗口日益狭窄,芯片抗击静电能力持续减弱,这对防护设计提出了更高要求。静电放电已成为半导体器件最常见的失效机理之一。在芯片设计阶段,必须充分考虑被防护器件的抗静电能力,合理选择ESD防护方案,以保障芯片在贴装、测试、转运及最终应用过程中免受ESD损伤。

发表评论 取消回复