一集成电路与片上系统的发展

在现代集成电路制造中,随着技术的不断进步,芯片的集成度越来越高,这使得失效分析成为了确保产品可靠性和性能的关键步骤。特别是对于内嵌式存储器,如电可擦可编程只读存储器(EEPROM),其结构的复杂性和高密度特性使得传统的失效分析方法难以准确定位失效模式和机理。本文将重点介绍一种基于栅氧化层损伤的EEPROM失效分析方法,该方法能够有效地定位和分析栅氧化层的微小缺陷,提高失效分析的成功率。

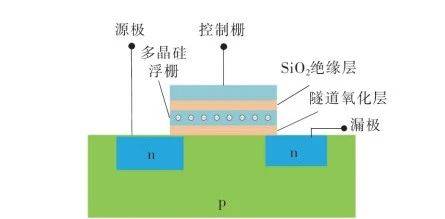

EEPROM基本单元结构示意图

二失效分析

首先,我们需要了解EEPROM的工作原理。EEPROM的工作原理基于浮栅隧道氧化层晶体管结构,通过电荷泵升压电路产生的高压电场,使得电荷能够在浮栅和漏区之间通过隧穿效应自由移动。这种结构使得EEPROM能够在浮栅中注入或释放电子,从而改变MOS晶体管的阈值电压,实现二进制数据的存储。

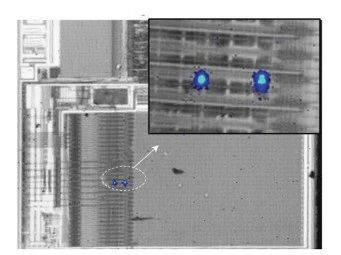

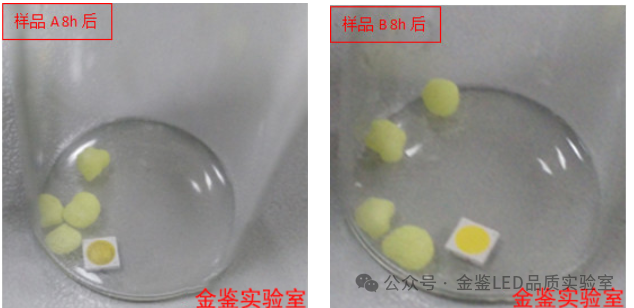

失效分析首先进行无损分析,包括外部目检、X射线检查等,若未发现异常,则进行有损分析。在有损分析中,红外发光显微镜(EMMI)是一种非常有效的工具。EMMI的工作原理是基于半导体内部电子跃迁过程中的红外发光现象来进行缺陷定位。通过对比失效样品和合格样品的红外EMMI图像,我们可以发现失效样品的EEPROM模块区域存在异常亮点,这表明该区域发生了电子-空穴对复合的漏电现象。

失效样品的红外 EMMI 照片

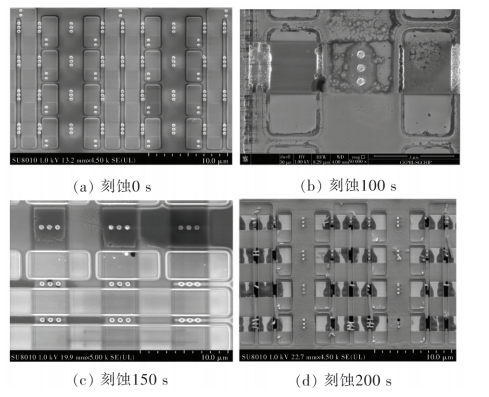

接下来,我们采用物理去层及观察的方法来确定漏电位置。去层过程通常采用反应离子刻蚀(RIE)方法去除钝化层和绝缘介质层,而对于金属层的去层,则可能采用手动研磨或离子束刻蚀(IBE)方法。在去层过程中,利用光学显微镜或扫描电子显微镜(SEM)进行观察和检测,可以发现漏电位置的晶体管部分通孔存在异常亮度,这表明下层电路存在漏电。

为了进一步确认漏电位置,我们采用电压衬度(VC)技术。VC技术利用样品表面电势差异对其表面的二次电子发射率产生影响,通过调整样品表面的二次电子发射,产生明暗对比明显的图像。通过VC图像,我们可以确认某处晶体管的栅极存在漏电或短路情况。

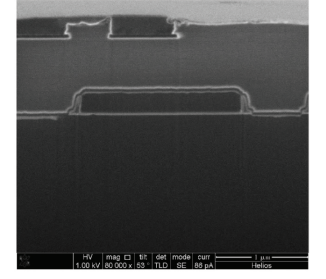

失效样品 FIB 剖面图

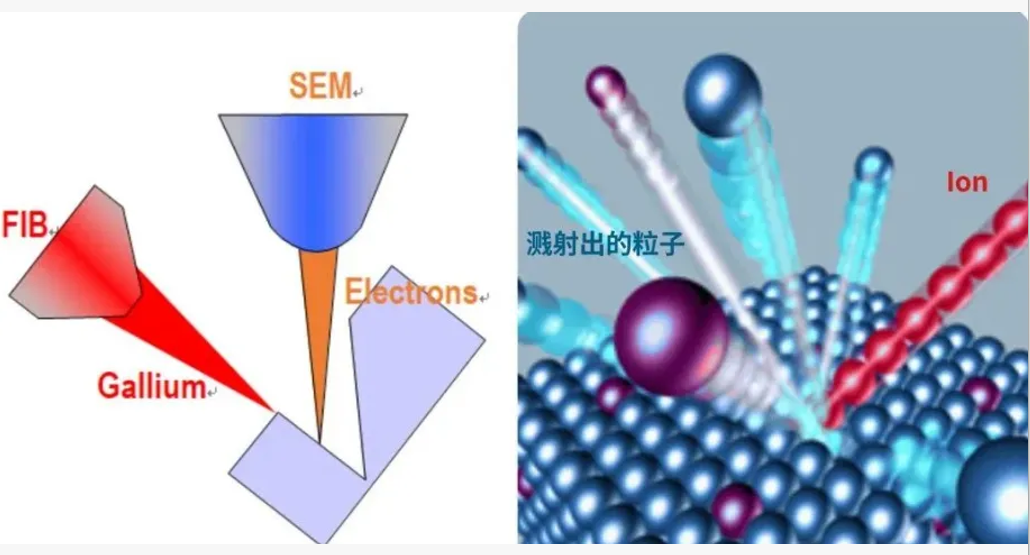

聚焦离子束(FIB)切面分析是一种高精度的切割工具,它可以在微米甚至纳米尺度上对芯片表面进行局部截面切割。金鉴实验室提供的Dual Beam FIB-SEM业务,包括透射电镜(TEM)样品制备,材料微观截面截取与观察、样品微观刻蚀与沉积以及材料三维成像及分析等,进一步扩展了FIB技术的应用范围。

通过FIB对VC发亮的区域进行切割,可以获得晶体管的截面图像。然而,由于FIB切割的幅度限制,可能无法发现尺寸较小的缺陷。

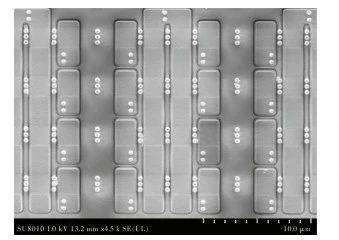

因此,采用化学刻蚀分析方法,利用多晶硅层和栅氧化层在氢氟酸中的不同反应速率,精确刻蚀多晶硅浮栅而保留栅氧化层。通过SEM观察,确认栅氧化层击穿损伤。

多晶硅层的 SEM 形貌

三失效机理分析与结论

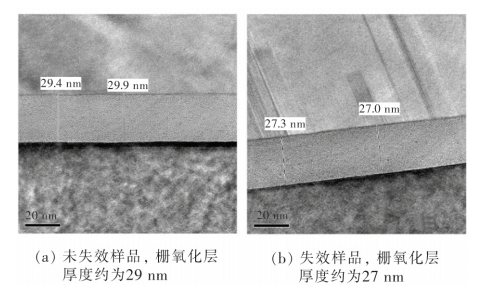

通过透射电子显微镜(TEM)对失效点的栅氧化层厚度进行测量,我们发现失效样品的栅氧化层厚度相比于合格芯片薄2~3纳米。由于栅氧化层厚度与存储单元耐压能力有直接关系,因此推断是由于工艺波动导致失效样品栅氧化层厚度偏低及耐压能力下降,在长时间应用后出现栅氧化层被击穿的问题。

刻蚀不同时间后的刻蚀效果 SEM 图

本文提出的化学刻蚀分析方法为集成电路失效分析提供了一种新的、高效的解决方案。这种方法不仅成本低、操作简便,而且能够有效减少分析时间并提高失效分析的成功率。随着集成电路技术的不断进步,这种分析方法有望在更广泛的应用领域中发挥重要作用,为提高集成电路的质量和可靠性做出贡献。

发表评论 取消回复