AEC-Q102标准是由汽车电子委员会(Automotive Electronics Council)制定的,目的是确保汽车电子元件在极端环境下的可靠性和稳定性。锡须试验是该标准中的一项关键测试,用于评估元件在长期使用过程中可能产生的锡须问题。金鉴实验室作为国内领先的光电半导体失效分析科研检测机构,具备执行AEC-Q101和AEC-Q102标准下的全部测试项目的能力,并且拥有一支由国家级人才工程入选者和资深技术专家组成的团队,以及先进的检测设备,确保了测试结果的准确性和可靠性。

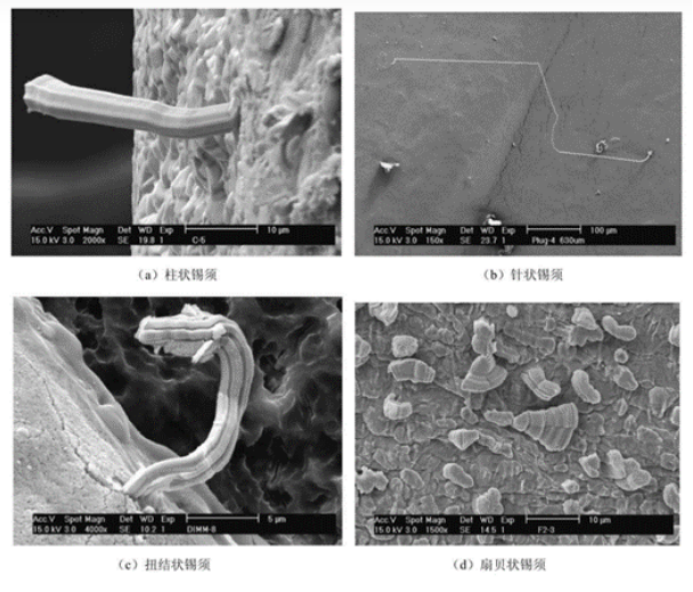

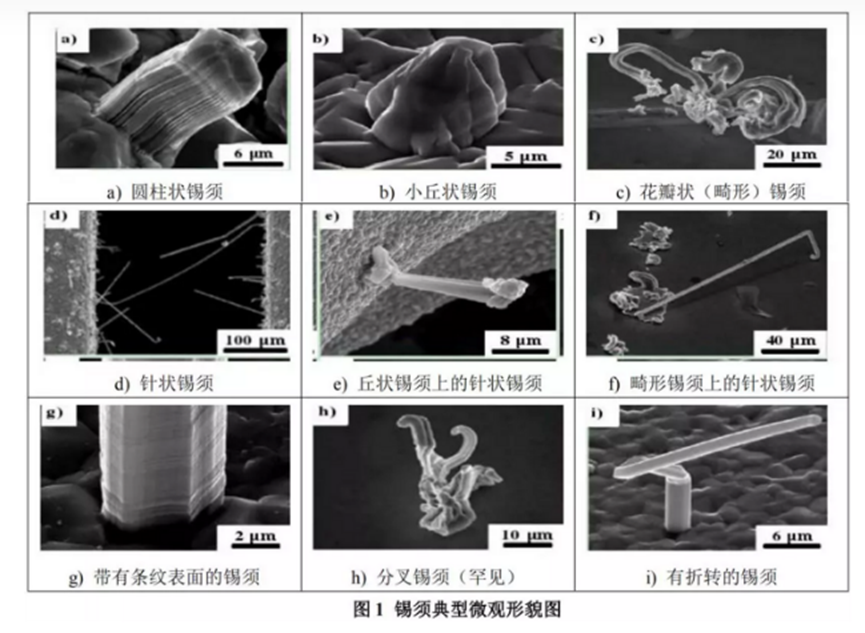

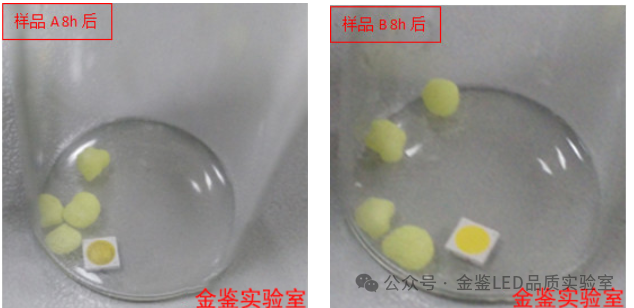

锡须是电子元器件焊接表面可能生长的细小锡晶须,可能导致电路短路、故障甚至失效。锡须试验通过模拟元器件在高温高湿环境下的运行情况,来评估焊点是否会产生锡须,从而影响其可靠性。锡须有以下类型:

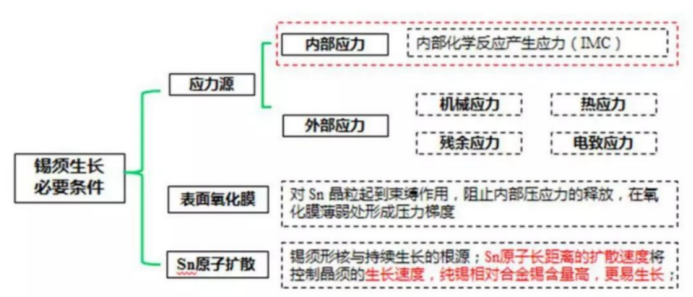

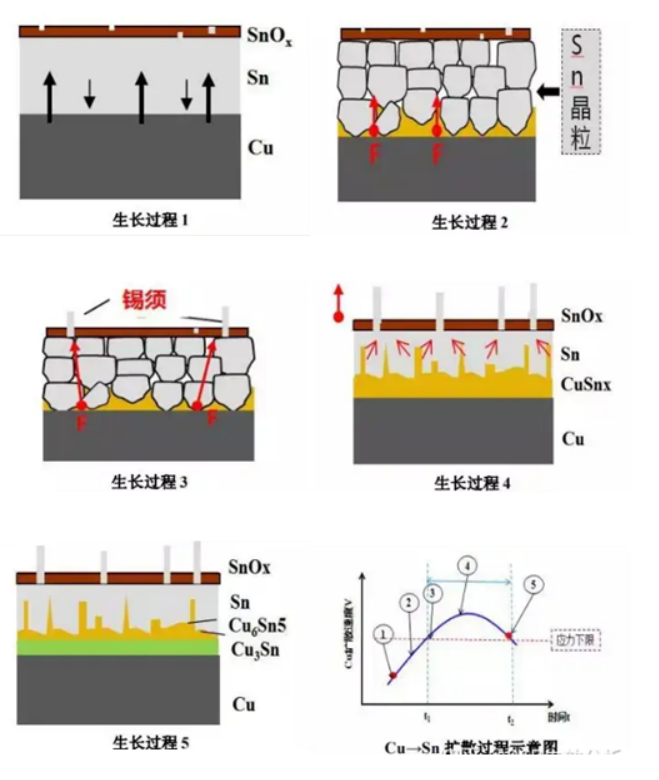

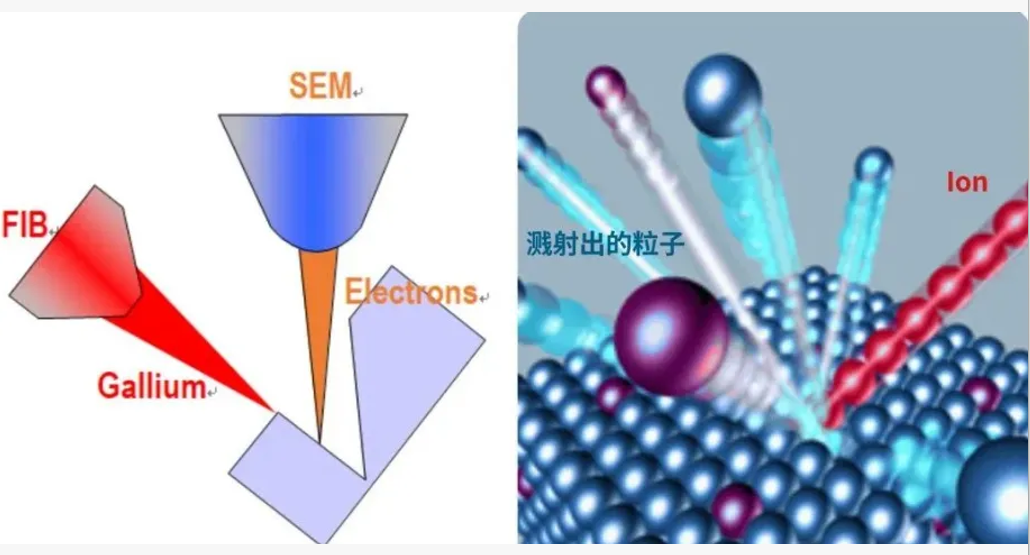

锡须的形成机理较为复杂,普遍认为与压应力生长有关。锡须生长需要应力源、Sn表面氧化层的束缚作用以及Sn原子的长范围扩散。锡须的生长过程包括Cu/Sn结合界面的原子扩散、Cu6Sn5的形成、压应力的产生、锡须的突破生长以及最终的生长减缓和停止。

为了抑制锡须的生长,可以采取多种方法,包括使用合金镀层替换纯锡镀层、进行退火处理以消除残余应力、在Cu上先镀Ni再镀Sn、选择合适的镀层厚度以及优化镀液和镀敷工艺。

锡须试验对于提高汽车电子元件的可靠性至关重要,它可以帮助制造商评估元器件在实际使用中可能出现的问题,提高产品的可靠性和稳定性。符合AEC-Q102标准的元器件在通过锡须试验后,能够获得更广泛的汽车电子应用认可,满足汽车行业对高品质电子元件的需求。

发表评论 取消回复