什么是CDM?

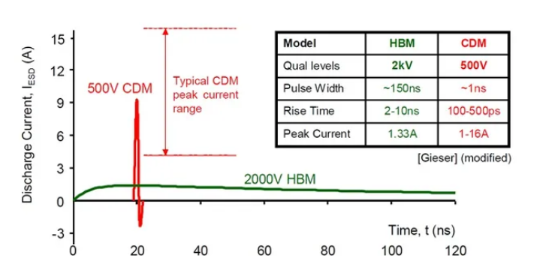

CDM(Charged Device Model)是一种用于评估电子元件在静电放电(ESD)条件下的敏感度的测试模型。与HBM(Human Body Model)和MM(Machine Model)不同,CDM模型关注的是电子元件在制造或运输过程中可能积累的电荷。当这些元件接触到地或其他导体时,电荷会迅速释放,形成快速的电流脉冲。

CDM测试:

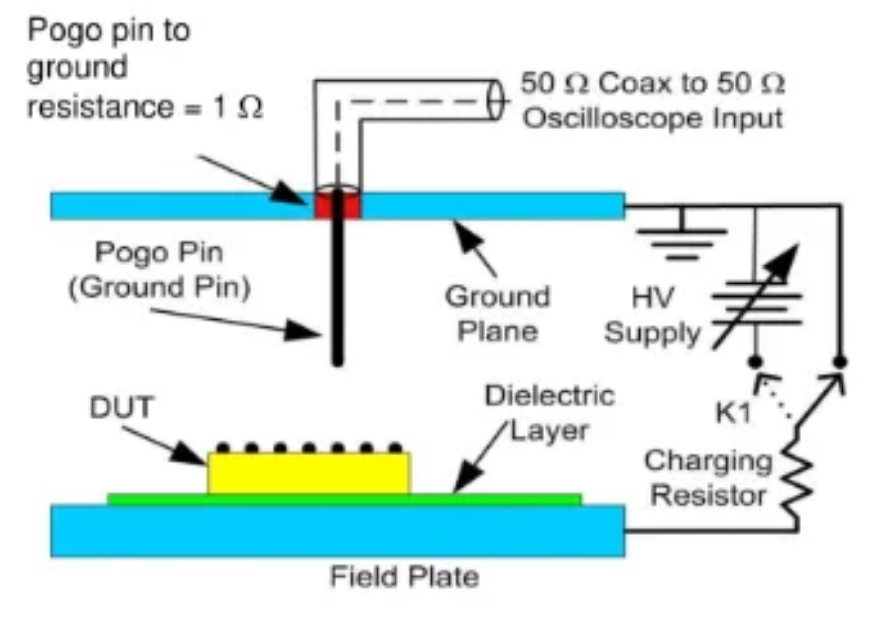

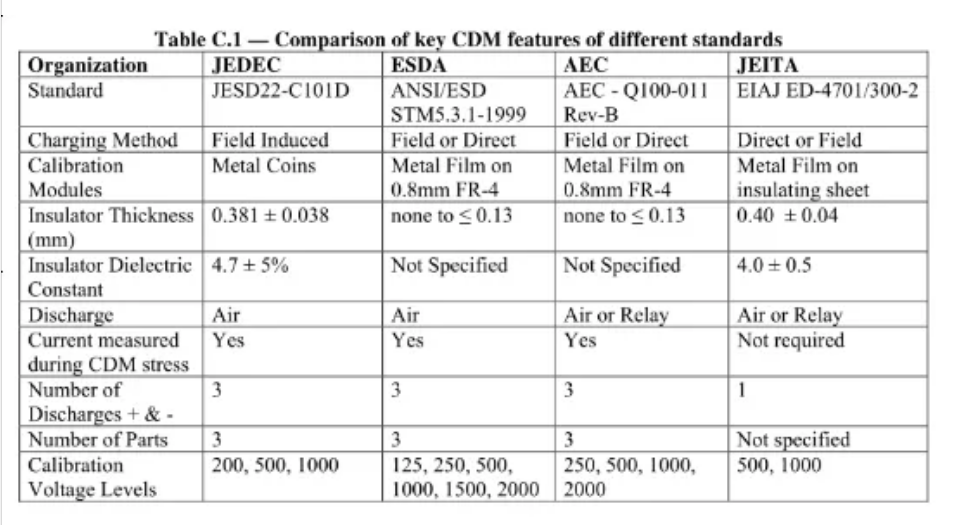

CDM测试通常包括一个充电板和一个可以移动到待测元件(DUT)引脚之间的接地探针。测试设备的设计允许模拟实际使用中可能遇到的静电放电情况。测试的标准和要求随着技术的发展而不断更新,以适应IC芯片性能的提升和封装尺寸的增大。

实际测试各模块

随着IC技术的进步,特别是对于更高速的IO性能的需求,维持推荐的CDM级别变得越来越具有挑战性。由于不同测试仪器的充电电阻存在差异,CDM目标级别可能需要根据ESD协会的建议进行调整。金鉴实验室意识到这一点,并致力于帮助客户评估其产品在面对静电放电时的表现。

测试标准的降低通常与以下因素有关:

1. IC元件的引脚数和封装尺寸的显著增长,导致在相同预充电压下,峰值电流限制了芯片的CDM能力。

2. IC工艺技术的进步,随着工艺尺寸的减小,CDM能力降低,因为更小的有源器件和更薄的金属互连降低了ESD电路的稳健性。

3. 高速数字、射频模拟和其他性能敏感引脚的混合信号IC的普及,要求在ESD保护和射频功能之间找到平衡。

CDM ESD目标级别的分布预期的变化

发表评论 取消回复