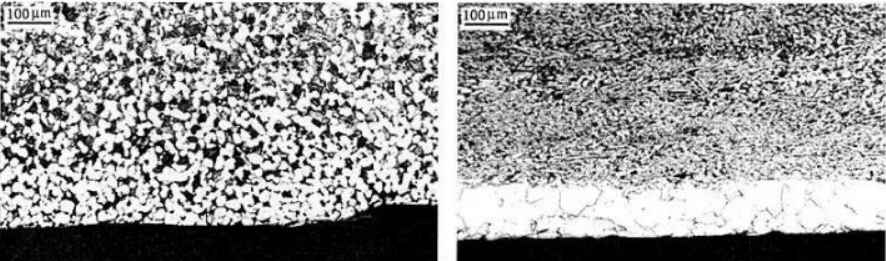

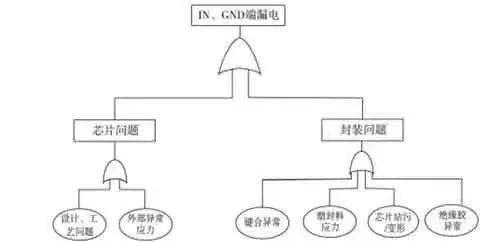

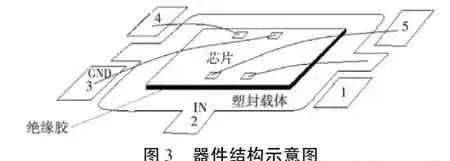

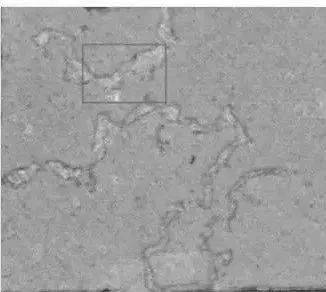

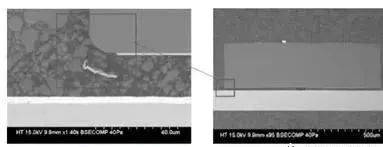

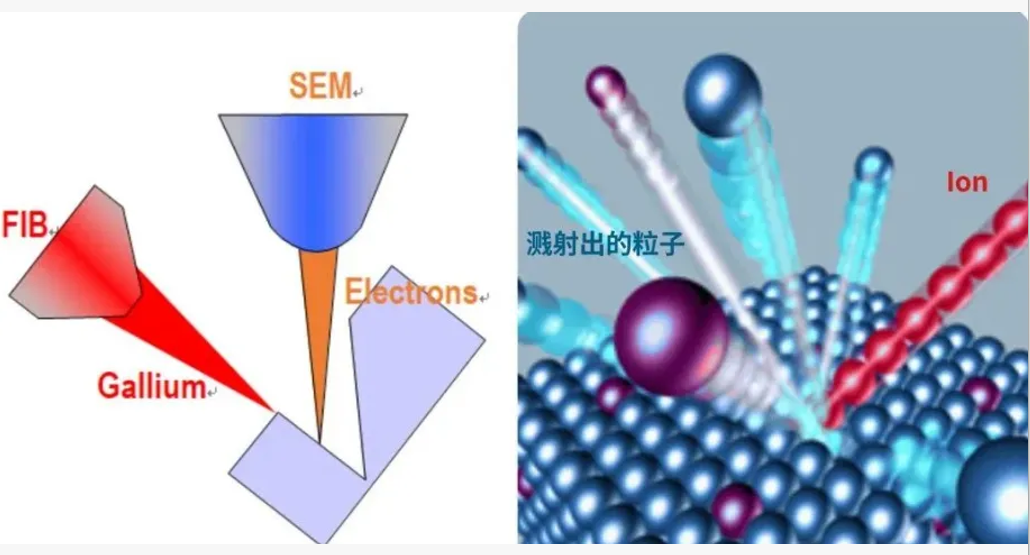

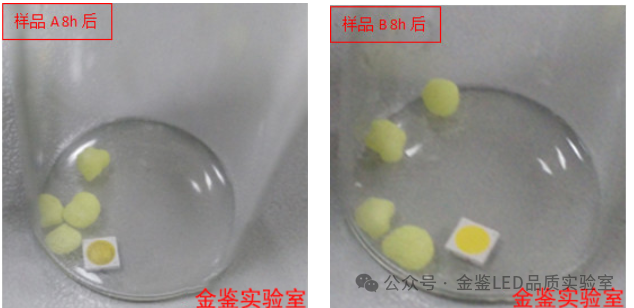

前言 ·失效现象 本文的器件样品是一种非门塑封器件,该器件经历了老炼(125℃,96h),温度冲击(-55℃~70℃、10次循环),高低温存储(-40℃~60℃),温度循环(-40℃~60℃,5次5h)等试验后,器件的性能合格。但是,在交变湿热试验 在第一次测试中,输入端对地短路,但在将样品在常温环境下放置约48小时后,第二次测试显示输入端对地的阻抗恢复正常(在MΩ级别)。进行温度循环试验后,第三次测试结果显示器件仍然合格,未出现失效。进一步对样品进行低温存储后的测试显示,在第四次测试中,电路输入端对地之间出现漏电,阻值约为40kΩ(正常值应大于20MΩ)。这表明失效样品的两个引脚之间的阻抗不稳定,间歇性出现小于MΩ级的阻抗值,从而影响了器件的性能。 ·失效原因分析 根据该样品塑封结构和内部电连接情况判断,造成输入端对地之间的漏电失效原因如图1所示。原因可能有芯片内部异常、芯片玷污或变形、键合丝异常、塑封应力较大、绝缘胶异常等。 1、芯片问题 2、封装问题 图二 失效样品 塑封器件的芯片表面覆盖着塑封料,该塑封料可能对芯片施加应力,从而导致器件失效的情况。通过采用机械方法去除芯片表面的塑封料,并对引脚间的阻抗进行测试,实验发现失效样品的输入端与地之间存在漏电现象。这表明,即使塑封应力消除后,失效问题并未完全消失,从而排除了芯片表面塑封料应力导致失效的可能性。 另外,芯片表面的玷污或变形也可能导致芯片短路的情况。通过在高倍显微镜下观察芯片表面,实验室未发现失效芯片表面有玷污或变形的现象,因此排除了芯片玷污或变形导致电路短路的可能性。进一步分析器件塑封结构示意图如图3所示,可以看出,芯片衬底电位为地,塑封载体连接输入端电位,而芯片底部与塑封载体之间通过绝缘胶隔离。 通常情况下,绝缘胶能够有效隔离电位,即输入端与地之间不存在电流通路。然而,如果绝缘胶存在异常,其绝缘性能会下降,导致输入端与地之间产生漏电,从而影响器件的性能。通过采用机械方法去除失效样品的塑封基板,并测试其输入端与地之间的I-V特性,实验发现漏电现象消失。因此,可以推断漏电通路位于衬底和基板之间的绝缘胶部位。 综上分析,确定失效样品输入端与地之间的漏电故障是芯片与基板之间的绝缘胶异常所致。 ·失效机理分析 失效样品的芯片与基板之间采用了绝缘胶来隔离输入端与地之间的电位。绝缘胶的厚度和质量对器件的输入端与地之间的绝缘效果有着重要影响,直接影响输入与地之间的阻抗值。 对失效样品和良品电路进行剖面分析,并对器件中的绝缘胶对比检查,发现失效样品比良品电路的芯片粘胶即绝缘胶的空洞更大,如图4所示。潮湿环境下,绝缘胶空洞所在位置容易发生爬电现象,使绝缘胶的绝缘强度进一步下降,最终导致输入端和地之间的绝缘胶产生漏电。 ·改进措施 目前,工业级塑封无法完全消除绝缘胶产生空洞的情况。为避免绝缘胶中产生空洞、芯片背金层脱落混入绝缘胶等引起器件失效的问题,可从器件结构设计方面采取相应措施,以提升器件的可靠性。结合器件的失效分析情况,金鉴实验室提出以下器件结构设计的建议: 准确定义器件各引脚之间的电位关系:建议在设计阶段准确定义器件各引脚之间的电位关系,尽量避免使用绝缘胶隔离不同电位。确保绝缘胶粘结两端的电位相同时,绝缘胶仅起粘结作用,即使出现轻微的绝缘胶漏电,也不会影响器件的可靠性。这一方法可从源头上避免绝缘胶异常导致的器件失效。去除背金层:针对背金层无明确用途的器件,在需要使用绝缘胶粘结时,建议尽量去除背金层后再使用。这样可以避免背金层在粘结过程中脱落混入绝缘胶,降低绝缘胶绝缘性能下降的风险。 增加绝缘胶厚度和添加绝缘颗粒:建议在使用绝缘胶粘结器件时,根据实际情况适当增加绝缘胶的厚度,并在绝缘胶中添加绝缘颗粒,以精确控制胶层的厚度均匀性。这种方法可以有效避免绝缘胶厚度不均匀导致的漏电问题,提高器件的可靠性。以上建议旨在优化器件结构设计,提升器件的可靠性,降低绝缘胶异常导致的失效风险。 ·结论 在部分工业级塑封器件中,绝缘胶产生空洞、掺有金属杂质等异常情况可能导致绝缘胶异常,进而在温度和湿度应力下引发漏电问题,甚至导致器件功能失效。在设计高可靠性的器件时,需要特别关注绝缘胶不达到理想绝缘的情况。

塑封器件绝缘胶漏电失效机理分析与改进措施

于 2024-06-21 12:45:01 发布

1354 阅读

0 评论

0 点赞

发表评论 取消回复